## УДК 004.272

**А.Н. ЛЫСЕНКО**, д.т.н., проф. каф. КЭВА, НТУУ "КПИ", Киев, **А.Ю. РОМАНОВ**, аспирант, асс. каф. КЭВА, НТУУ "КПИ", Киев

## РЕСУРСОЭФФЕКТИВНЫЙ РОУТЕР ДЛЯ МНОГОПРОЦЕССОРНОЙ СЕТИ НА ЧИПЕ

Рассмотрены различные подходы к организации сетей на чипе. Выявлен основной недостаток сетей на чипе с коммутацией пакетов — чрезмерно большие объемы входных и выходных буферов роутеров. Предложена новая архитектура роутера с улучшенными показателями потребляемых ресурсов и высоким быстродействием. Ил.: 5. Библиогр.: 12 назв.

Ключевые слова: сеть на чипе, коммутация пакетов, буфер, архитектура роутера.

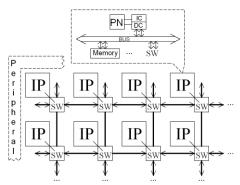

Постановка проблемы. Развитие полупроводниковых технологий привело к тому, что огромное количество транзисторов, доступное на одном кристалле FPGA, позволяет разработчикам интегрировать десятки ІР-ядер в одну многопроцессорную систему [1]. Такие системы на чипе (MPSoC), благодаря параллельной обработке потоков данных имеют большое быстродействие и пропускную способность, что и обусловило их перспективность и популярность. Однако с увеличением количества вычислителей на одном чипе значительно возросли требования к подсистеме связи по пропускной способности, потребляемым ресурсам и т.д., а такие классические подходы как односвязная архитектура и общая шина стали неэффективны [1 – 4]. Решением проблемы стало появление концепции объединения вычислительных ядер в сеть - NoC (Network-on-Chip). Сутью данного подхода является объединение IP-ядер, обычно представляющих собой процессорное ядро (PN) с локальной памятью и дополнительными устройствами, с помощью специализированных роутеров – SW (switch) [2] (рис. 1).

Рис. 1. Типовая структура сети на чипе

Преимущество данной концепции перед классическими состоит в том, что короткие соединения точка-точка между роутерами обеспечивают малую паразитную емкость и высокую частоту работы благодаря наличию промежуточных регистров на пути прохождения сигнала, а данные в различных сегментах сети передаются и коммутируются одновременно [3]. Это обеспечивает высокую производительность, пропускную способность и экономию ресурсов, что делает исследования и разработку новых архитектур сетей на чипе актуальными.

Анализ литературы. Наиболее распространенной архитектура сетей на чипе с коммутацией пакетов, где обычно whormhole-технология соединения применяется кредитным управлением потоком и ХУ – маршрутизацией [2, 4 – 8]. Главным недостатком таких систем является необходимость в буферизации соединений на входе, а иногда и на выходе, что приводит к большим затратам ресурсов. Уменьшение объема буферов малоэффективно и чревато потерей производительности. В работах [9, 10] предложены реализации сетей на чипе с коммутацией на уровне цепей, при этом экономия ресурсов достигается за счет отсутствия буферизации. В этих подходах падение быстродействия происходит из-за того, что на время передачи данных резервируется полный путь от источника до адресата и блокируются другие передачи [11].

Таким образом, на фоне многообразия различных вариантов реализаций сетей на чипе существует большая потребность в разработке новых архитектур и их составных элементов, обеспечивающих высокую пропускную способность при минимальных ресурсных затратах. Кроме этого, свой отпечаток накладывает тот факт, что данное направление электронике является сравнительно новым В И недостаточно разработанным, проектов коммерческими, большинство отсутствующую сориентированными Украине на В технологию ASIC [1, 3, 4, 6], а FPGA реализации – на платформу Xilinx [7, 8].

**Цель статьи** — разработка новой схемы роутера с низкими требованиями к объему буферных элементов и высоким быстродействием для сетей на чипе на базе FPGA платформы фирмы Altera.

**Используемая архитектура сети на чипе.** Авторами выбрана в качестве рабочей архитектура тороидальной сети на чипе с коммутацией пакетов. Выбор данной топологии обусловлен ее простотой и эффективностью, а также идентичностью структур роутеров [2, 5, 11, 12]. Применение технологии с коммутацией на уровне пакетов обусловлено

ее большей эффективности в сравнении с коммутацией на уровне цепей [11]. Поскольку предполагаемое количество IP-ядер составляет не более 16 и задержки синхросигнала будут незначительные, выбрана сеть с глобальной синхронизацией.

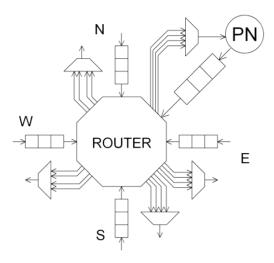

**Предлагаемая архитектура роутера.** Наиболее распространенная архитектура роутера для сетей на чипе приведена на рис. 2.

Рис. 2. Классическая структура роутера

Роутер представляет собой коммутационную матрицу, направляющую на соответствующие выходы потоки флитов, накапливаемые во входных буферных элементах (N, E, S, W) [2, 5, 7, 11]. Кроме входов, буферные элементы также могут присутствовать и на выходах роутера, их размер варьируется в зависимости от требуемой пропускной способности и длины пакетов. Использование такой архитектуры приводит к большим ресурсным затратам энергопотреблению, а из-за неравномерного характера загрузки сети значительная часть буферных элементов может простаивать.

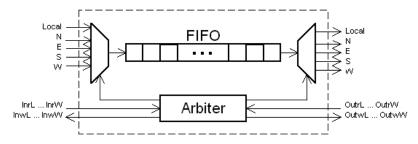

С целью устранения недостатков описанной выше архитектуры и уменьшения буферной памяти авторами предложено разделение функции коммутационной части роутера на входной и выходной блоки, соединенные между собой буферной памятью типа FIFO (First Input First Output) объемом в 16 флитов (рис. 3).

Рис. 3. Предложенная структура роутера

Управление коммутацией с локальным IP-ядром и соседними роутерами (N, E, S, W) осуществляет распределенный арбитр с помощью сигналов разрешения и подтверждения приема/передачи (Inr-InrW, InwL-InwW, OutrL-OutW, OutwL-OutwW). Очевидно, что предложенная сеть на чипе относится к классу сервиса с лучшей пропускной способностью и FCFS (First Come First Serve) арбитражем [2, 5, 11].

Входной и выходной коммутационные модули роутера созданы на высокоуровневом языке описания аппаратуры Verilog, а модуль FIFO взят из библиотеки мегафункций среды проектирования Quartus II фирмы Altera, поскольку разрабатываемая сеть на кристалле ориентирована на FPGA данной фирмы. Кроме того, реализации стандартных мегафункций универсальны, легко настраиваемы, что облегчает процесс проектирования, и написаны на низкоуровневом языке AHDL. Это делает их более компактными, быстродействующими и оптимизированными под архитектуру ПЛИС в сравнении с аналогичными реализациями на других языках.

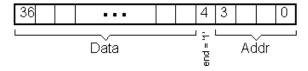

Особенности алгоритма передачи данных. Адрес назначения сообщений формируется по месту их генерации и является однонаправленным. Сами сообщения разбиваются на пакеты длиной от 1 до 8 флитов каждый. Флит состоит из 32 бит данных, дополнительного бита, единичное значение которого идентифицирует, что данный флит последний в пакете, а также 4 адресных битов (рис. 4).

Рис. 4. Структура флита

Таким образом, в сети может быть до 16 роутеров, каждому из которых присвоен уникальный адрес.

Принятие решения о коммутации пакетов осуществляется по классическому детерминистическому алгоритму XY, т.е. сначала пакеты распространяются по сети в горизонтальном направлении, а потом — в вертикальном. Очевидно, что данный алгоритм охватывает только часть возможных путей прохождения пакетов (partial), хотя и направляет пакеты всегда с приближением к цели (profitable) [11].

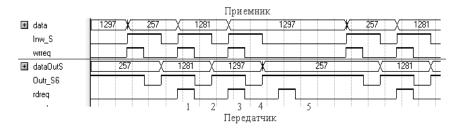

Передача данных осуществляется с подтверждением (рис. 5).

Рис. 5. Прием/передача данных

Передатчик проверяет наличие в FIFO данных, генерирует сигнал чтения и получает один флит (шаг 1), анализирует адрес назначения, согласно с алгоритмом XY выставляет данные на соответствующий порт и генерирует сигнал запроса на передачу (шаг 2). В свою очередь, приемник соседнего роутера при наличии места в FIFO анализирует сигналы запроса на передачу, фиксирует одно из направлений и коммутирует данные на вход FIFO, генерируя сигнал записи (шаг 3). Одновременно передатчик сбрасывает сигнал передачи и готовится к следующей итерации, генерируя сигнал чтения из FIFO. По завершении приема приемник генерирует сигнал подтверждения передачи и готовности принимать следующий флит (шаг 4). Кроме того, он анализирует епd-бит флита, и если это конец пакета, прежде чем продолжить прием данных с текущего направления, проверяет наличие запросов с других направлений, во избежание длительных блокировок (шаг 5).

Апробация. Разработанный роутер был синтезирован в среде проектирования Quartus II для FPGA Cyclone II, занимает 250 Les, 592 бита памяти. При этом статическое и динамическое потребление энергии составило соответсвенно 40,43 мВт и 81,44 мВт, а максимальная частота работы — 200 МГц. Так как минимальное время прохождения флита составляет 3 такта (рис. 5), а его информативная часть — 32 бита, то

пропускная способность роутера достигает ~2,13 Гбит/с, что соизмеримо с существующими аналогами [7, 8], при значительно меньших ресурсных затратах. При этом в зависимости от базовой платформы FPGA тактовая частота может быть значительно выше (например, 310 МГц для Stratix II).

новую Выводы. Предложено архитектуру роутера ДЛЯ многопроцессорной сети на чипе с коммутацией пакетов, отличительной которой является разделение функции коммутационной части на входной и выходной блоки, соединенные между собой буферной памятью типа FIFO. Это позволило в сравнении с указанными выше аналогами в несколько раз уменьшить затраты ресурсов на организацию буферных элементов, сохранив при этом показатели быстродействия.

Перспективным направлением дальнейших исследований является усовершенствование роутера путем введения виртуальных каналов, уменьшения времени прохождения флита до 2 тактов, разнесение приемника и передатчика на разные фронты тактовой частоты.

Список литературы: 1. Пат. 03013591A1 U.S., МПК G06F17/50. Method to design networkon-chip (NOC) - based communication systems / Murali S., Benini L., De Micheli G.; заявитель и патентообладатель EPFL (CH). - заявл. 10.10.2006; опубл. 28.01.2009. 2. Axel J. Networks on Chip / J. Axel, T. Hannu // Kluwer Academic Publishers. - Dordrecht, 2003. - 303 p. 3. Angiolini F. A layout-aware analysis of networks-on-chip and traditional interconnects for mpsocs / F. Angiolini, P. Meloni, M.S. Carta // IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems. – 2007. – Vol. 26. – № 3. – P. 421–434. 4. Benini L. Network-onchip architectures and design methods / L. Benini, D. Bertozzi // Computers and Digital Techniques. - IEEE Proc., 2005. - Vol. 152. - No. 2. - P. 261-272. 5. Bjerregaard T. A survey of research and practices of Network-on-chip / T. Bjerregaard, S. Mahadevan // ACM Computing Surveys. -2006. – Vol. 38(1). – 51 p. **6.** *Rijpkema E*. Trade-offs in the design of a router with both guaranteed and best-effort services for networks on chip / E. Rijpkema, K.G.W. Goossens, A. Radulescu. - IEEE Proc., 2003. - Vol. 150. - №. 5. - P. 294–302. 7. Moraes F.G. HERMES: an Infrastructure for Low Area Overhead Packet-switching Networks on Chip / F.G. Moraes, N.L.V. Calazans, A.V. Mello // Integration, the VLSI Journal. - 2004. - Vol. 38. -No. 1. - P. 69-93. 8. Marescaux T. Interconnection Networks Enable Fine-Grain Dynamic Multi-Tasking on FPGAs / T. Marescaux // FPL'02. - 2002. - P. 795-805. 9. Phi-Hung P. High Performance and Area-Efficient Circuit-Switched Network on Chip Design / P. Phi-Hung // IEEE CIT'06. - 2006. - P. 243. 10. Wolkotte P.T. An Energy-Efficient Reconfigurable Circuit-Switched Network-on-Chip / P.T. Wolkotte, G.J.M. Smit, G.K. Rauwerda. - IEEE Proc. IPDPS, 2005. -Vol. 4. – P. 155a. 11. Ankur A. Survey of Network on Chip (NoC) Architectures & Contributions / A. Ankur, I. Cyril, S. Ravi // Engineering, Computing & Architecture. - 2009. - Vol. 3(1). - 15 p. 12. Романов О.Ю. Аналіз топологій мереж на чипі / О.Ю. Романов // Сучасна інформаційна Україна: інформатика, економіка, філософія: матеріали доповідей конференції, 13-14 травня 2010 р. – Донецьк, 2010. – Т. 1. – С. 407–410.

## УДК 004.272

Ресурсоефективний роутер для багатопроцесорної мережі на чипі / Лисенко О.М., Романов О.Ю. // Вісник НТУ "ХПІ". Тематичний випуск: Інформатика і моделювання. — Харків: НТУ "ХПІ". -2011. — № 17. — С. 86-92.

Розглянуто різноманітні підходи щодо організації мереж на чипі. Виявлено основний недолік мереж на чипі з комутацією пакетів — надмірно великі обсяги вхідних і вихідних буферів роутерів. Запропоновано нову архітектура роутера з поліпшеними показниками споживаних ресурсів і високою швидкодією. Іл.: 5. Бібліогр.: 12.

Ключові слова: мережа на чипі, комутація пакетів, буфер, архітектура роутера.

UDC 004.272

Resource efficient router for multiprocessor network on chip / Lisenko O.M., Romanov O.Y. // Herald of the National Technical University "KhPI". Subject issue: Information Science and Modelling. – Kharkov: NTU "KhPI". – 2011. – N. 17. – 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10. 1

Various approaches to networks on chip organizing are considered. The main drawback of networks on chip packet switching is identified – an excessively large buffers amounts of input and output buffers of routers. The new router architecture with improved resource consumption and high speed action is offered. Figs.: 5. Refs.: 12 titles.

**Keywords:** network on chip, packet switching, the buffer, router architecture.

Поступила в редакцию 07.02.2011